▼ 신한투자증권 반등의 역사 REPORT 시리즈

① 네 차례 Cycle의 교훈

[필독] 반도체 산업 리포트 : 반등의 역사 - 네 차례 Cycle의 교훈

▼ 신한투자증권 '반등의 역사' REPORT 시리즈 전편 반도체/장비 - 반등의 역사 ① (신한투자증권 : 고영민) 네 차례 반등의 역사가 말해주는 교훈 22~23 Cycle은 코로나19로 만들어진 IT 수요 거품이 급

feeling-stock.tistory.com

② 교훈의 적용, 23년 Cycle에 대한 해답 찾기

[필독] 반도체 산업 리포트 : 반등의 역사 - 교훈의 적용, 23년 Cycle에 대한 해답 찾기

▼ 신한투자증권 반등의 역사 REPORT 시리즈 전편 ① 반등의 역사 : 네 차례 Cycle의 교훈 [필독] 반도체 산업 리포트 : 반등의 역사 - 네 차례 Cycle의 교훈 ▼ 신한투자증권 '반등의 역사' REPORT 시리즈

feeling-stock.tistory.com

③ 중기적 메모리 Cycle 미리보기 – 공급

[필독] 반도체 산업 리포트 : 반등의 역사 - 중기적 메모리 Cycle 미리보기 (공급)

▼ 신한투자증권 반등의 역사 REPORT 시리즈 ① 네 차례 Cycle의 교훈 [필독] 반도체 산업 리포트 : 반등의 역사 - 네 차례 Cycle의 교훈 ▼ 신한투자증권 '반등의 역사' REPORT 시리즈 전편 반도체/장비 -

feeling-stock.tistory.com

④ 중기적 메모리 Cycle 미리보기 – 수요

[필독] 반도체 산업 리포트 : 반등의 역사 - 중기적 메모리 Cycle 미리보기 (수요)

▼ 신한투자증권 반등의 역사 REPORT 시리즈 ① 네 차례 Cycle의 교훈 [필독] 반도체 산업 리포트 : 반등의 역사 - 네 차례 Cycle의 교훈 ▼ 신한투자증권 '반등의 역사' REPORT 시리즈 전편 반도체/장비 -

feeling-stock.tistory.com

⑤ 새로운 수요의 중심, 비메모리

[필독] 반도체 산업 리포트 : 반등의 역사 - 새로운 수요의 중심, 비메모리

▼ 신한투자증권 반등의 역사 REPORT 시리즈 ① 네 차례 Cycle의 교훈 [필독] 반도체 산업 리포트 : 반등의 역사 - 네 차례 Cycle의 교훈 ▼ 신한투자증권 '반등의 역사' REPORT 시리즈 전편 반도체/장비 -

feeling-stock.tistory.com

반도체/장비 - 반등의 역사 ③ (신한투자증권 : 고영민)

중기적 메모리 Cycle 전망의 핵심, 공급

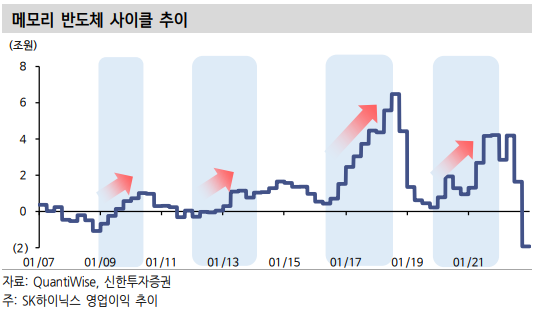

메모리 반도체에서 중요한 수요는 공급이 만드는 상대수요

1) 반도체 수요는 크게 두 가지 형태로 구분해 생각할 수 있으며, 절대적 규모의 수요와 상대적 규모의 수요임.

2) 상대적 규모의 수요는 기준점이 공급이며, 공급대비 수요가 어느정도인지가 메모리 반도체에서 중요하고 이는 과거의 모습을 통해 확인이 가능함.

3) 수요 호황으로 기억되고 있는 과거 Cycle 구간을 보면 공통적으로 이전 Down-Cycle의 영향이 컸으며, 당시 메모리 후발업체 구조조정(도산) 및 생산업체들의 자발적 공급 축소를 통해 절대적인 공급 수준은 낮아져 있었음.

4) Cycle의 상승 진폭 크기를 결정하는 것은 절대적인 수요의 확대 크기이나 시작은 공급에서 만들어지며, 결론적으로 Cycle을 결정하는 핵심변수는 공급이라는 것을 알 수 있음.

지난 50년간의 메모리 공급 & 공급업체 history

1) 1970~1990 : 일본의 메모리 전성기로 1970년 인텔이 DRAM을 개발한 이후, 일본 기업들도 뒤이어 메모리 반도체 시장에 진입했음.

2) 정부 지원속에서 판매가를 의도적으로 낮춰 파는 가격 인하 전략을 통해 경쟁을 이어갔고, 1985~1986년 인텔은 메모리 사업을 철수했음.

3) 1983년 삼성전자는 64K DRAM 개발에 성공하며 메모리 반도체 시장에 진입했으며, 일본의 저가 판매 전략으로 삼성전자도 적자가 이어졌으나 1986년 미국과 일본의 저가 반도체 수출금지 협정 이후 삼성전자 메모리 사업부의 턴어라운드가 시작됐음.

4) 1991~2000 : 삼성전자의 약진 & DRAM 산업 구조조정 시작시기로 1989년 삼성전자는 글로벌 최초 16M DRAM을 개발했고 1991년 최초 양산에 성공하는 등 본격적인 약진이 시작됐음.

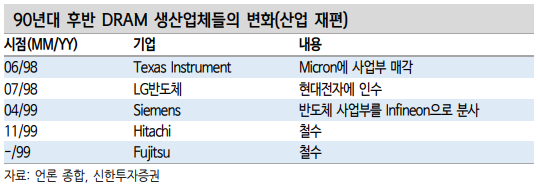

5) 90년대 후반부터는 DRAM 산업 구조조정이 시작됐으며, 일본 NEC와 히타치의 합작사인 엘피다의 탄생과 더불어 일본 업체들의 퇴출(파산)이 활발히 진행됐음.

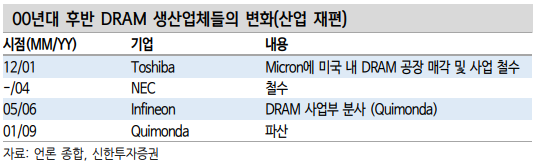

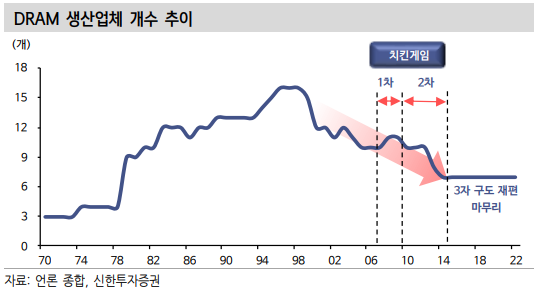

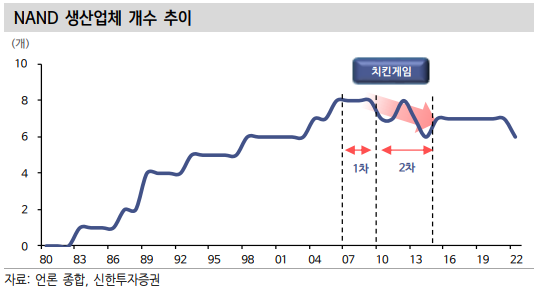

6) 2001~2010 : DRAM 산업 구조조정 지속 & 1차 치킨게임시기로 2004년 NEC가 철수할 때까지 일본 업체들의 구조조정은 지속됐음.

7) 이후 2007년부터 2009년까지 대만 업체들이 주도한 1차 치킨게임이 시작됐으며, 공격적 증설과 함께 가격 인하 전략을 펼치면서 DRAM 가격은 큰 폭 하락했음.

8) 후발주자들의 적자를 감내한 경쟁은 한계점에 도달했고, 독일 키몬다의 파산을 끝으로 1 차 치킨게임은 마무리됐음.

9) 2011~2015 : 2차 치킨게임시기로 2010년부터 2013년까지 2차 치킨게임이 진행됐으며, 대만과 일본 업체들의 주도로 시작됐음.

10) 1차와 마찬가지로 공급업체들의 재무 건전성은 악화됐고, NEC와 히타치의 합작사인 Elpida는 DRAM M/S 3위임에도 불구하고 파산하며 치킨게임이 종료됐음(Elpida는 이후 마이크론이 인수함).

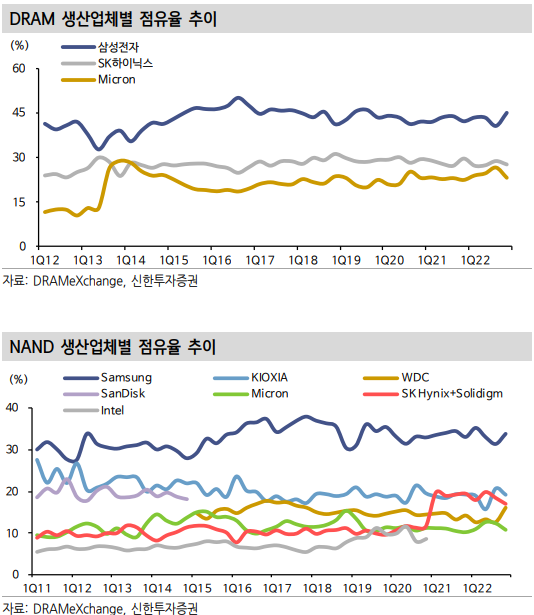

11) 2016~2020 : 3자구도 재편 마무리 & 중국 1차 반도체 굴기시기로 삼성전자, SK하이닉스, 마이크론 3자구도로 재편된 이후 치킨게임은 더 이상 발생하지 않았음.

12) 과거와 같은 점유율 싸움이 아닌 이익 극대화를 위한 공급 전략이 지속됐으며, 2016년 CXMT(DRAM), YMTC(NAND)가 설립되면서 1차 중국 반도체 굴기가 시작됐음.

13) 그러나 우려와 달리 3년간 유의미한 결과는 없었고 중국의 반도체 굴기는 일시적으로 정체기에 진입했음.

14) 2021~현재 : NAND 산업재편 추가 진행 & 중국 2차 반도체 굴기가 진행 중이며, 큰 변화 없는 DRAM과 달리 NAND에서는 산업재편이 추가로 진행되고 있음.

15) 2021년 말, SK하이닉스가 인텔의 NAND 사업부(Solidigm)를 인수했으며 최근에는 Western Digital과 Kioxia의 합병 가능성이 제기되고 있음.

16) 추가적인 재편 결과에 따라 현 점유율 구도의 변화가 발생할 전망이며, 정체기에 있던 중국 반도체 굴기는 2022년을 기점으로 활기를 찾는 모습임.

17) CXMT, YMTC를 비롯한 중국 현지 중소 생산업체들은 중국 지방정부의 지원금을 기반으로 투자를 확대 중이며, 과거와의 차이는 반도체 생산 능력이 진전됐다는 점이고 앞으로의 향방을 지켜봐야 할 필요성이 있음.

앞으로의 구조적 방향성은 제한적 공급 증가

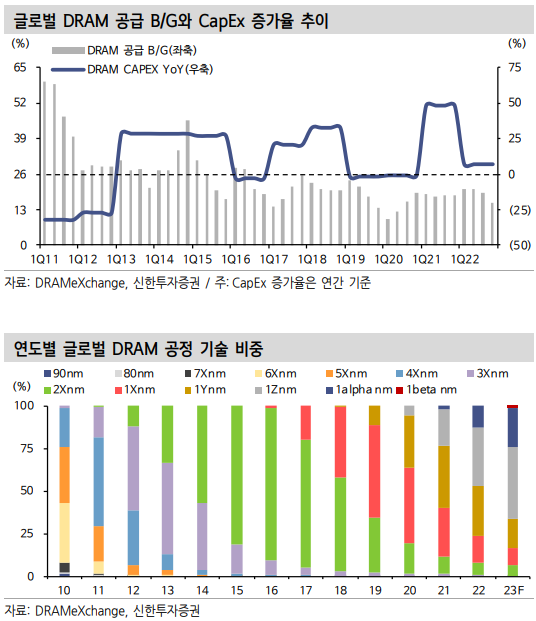

1) 반도체 생산업체들의 끝나지 않는 숙제는 집적도 향상이며, 웨이퍼 면적당 많은 칩을 생산하는 것이 중요함.

2) 이를 위해 미세화(선폭 줄이기) 노력이 지속되고 있으나 과거대비 공정기술 난이도가 증가했으며, 20~30나노와 비교했을 때 현재 14나노에서 13, 12 나노 등으로 선폭을 줄이는 것은 더디게 진행되고 있음.

3) 공급 증가율이 추세적으로 낮아지고 있는 배경이며, 물론 현 상황에서 공급을 증가시킬 수 있는 방법이 없지는 않음.

4) 선폭 줄이기가 더디게 진행됨에 따라 양산라인당 생산량은 감소하겠으나, 양산라인 자체를 늘린다면 공급을 증가시킬 수 있음.

5) 그러나 라인 증설은 곧 생산업체들의 CapEx 부담 증가를 의미하며, 이미 과거대비 Fab 건설비용, EUV 장비 등 고가의 장비 구매 등에 따라 절대적 CapEx 수준을 급격하게 증가시키는 것은 쉽지 않음.

6) 결국 공정 미세화 심화로 인해 확인되는 제한적 공급 증가는 구조적으로 지속될 수밖에 없다고 판단되며, 앞으로의 공급 방향성도 크게 다르지 않을 전망임.

관전 포인트, 중국 반도체 굴기 성공 or 실패?

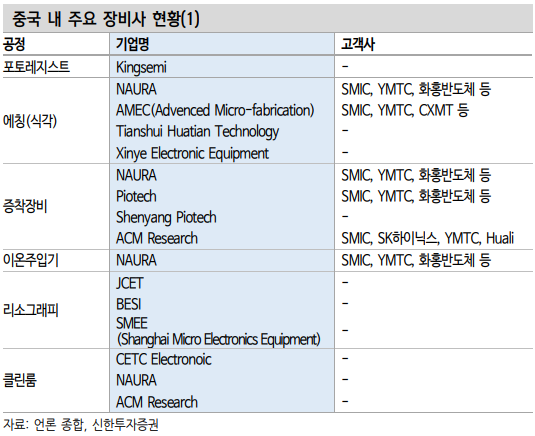

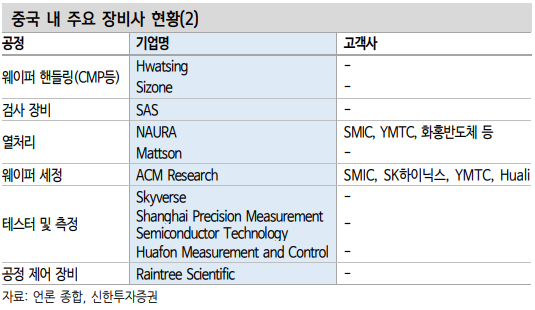

1) 미국의 제재로 현재 중국은 최선단 공정 구성을 위한 장비 조달이 원활히 진행 할 수 없으며, 레거시가 아닌 최선단 공정에 대한 진척도를 높이기 위해서는 주요 장비 조달이 필수적임.

2) 중국 반도체 굴기를 막아야 하는 미국 입장에서 관련 제재 강도는 지속적으로 높아질 수밖에 없으며, 결국 중국의 반도체 굴기 성공은 핵심 장비들에 대한 국산화 여부로 귀결됨.

3) 한국무역협회에 따르면, 중국 내 장비 국산화율은 22년 상반기 기준 32% 수준이며, 40나노 이상에서는 80%를 상회하는 국산화율을 보이고 있음.

4) 현지 장비사인 Naura, AMEC 등은 증착, 세정 등의 공정에서는 성과가 이미 확인되고 있으며, 공정 미세화의 핵심인 식각 공정에서도 확대를 진행 중임.

5) 중국 정부의 막대한 자금 지원과 이를 기반으로 과거와 달리 이미 장비사들의 기술 수준이 높아졌다는 점에서, 중국 내 생산업체들과 장비사들의 동향에 대해 지속적 관찰이 필요하다고 판단됨.

6) 중국 내에서 발생하는 IT 수요는 30~40% 이상으로 추정되고 중국이 자국 내 수요만 담당한다고 해도 작은 규모가 아니며 반대로 삼성전자, SK하이닉스 측면에서는 의미있는 비중의 수요를 일부 뺏기는 상황으로 전개될 수 있음.

공정기술 난이도 증가, 기술변화 방향성 살펴보기

공정 미세화 현황

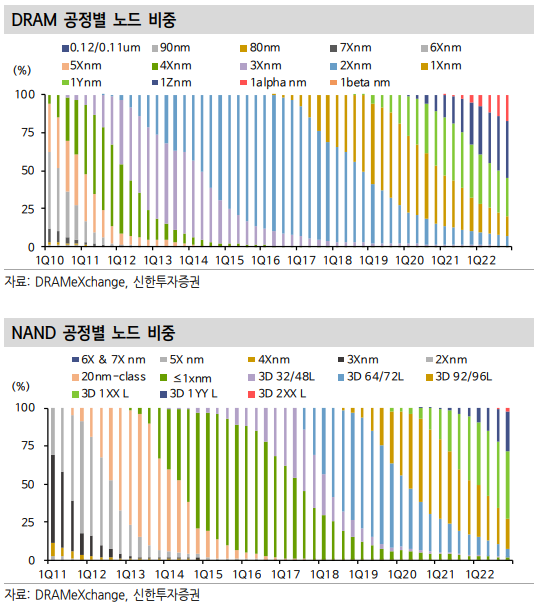

1) DRAM 기준, 현재 삼성전자, SK하이닉스, 마이크론 모두 1anm(13~15nm)가 최선단 기술이며, 일부 양산은 시작했고 대부분 수율 안정화 단계인 것으로 추정됨.

2) 당초 예상했던 것보다 차세대 1b, 1c에 대한 준비 진척도는 낮은 것으로 파악되며, 미세화 심화로 인한 산업 내 구조적인 흐름임.

3) NAND의 경우, 이미 일찍이 기존 2D 구조에서의 한계를 직면하고 3D 구조로 변화됐으며, 최근 NAND의 미세화는 단수 증가로 이어지고 있고 현재 최선단 기술은 176단이며 생산업체들은 차세대 232단을 준비 중에 있음.

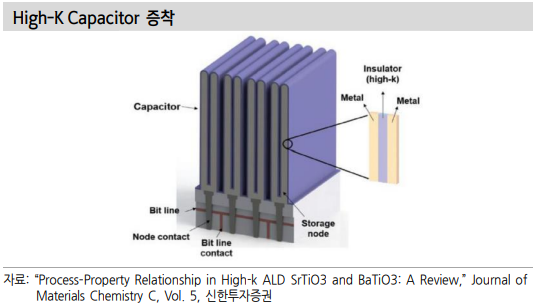

미세화 대응 방향 - ① High-K Capacitor 공정

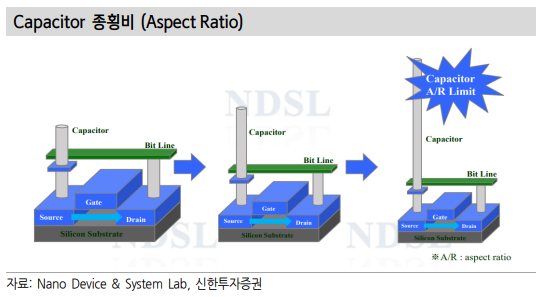

1) 미세화의 핵심은 선폭의 축소이며, 선폭의 축소는 채널의 거리 축소를 의미하는데 단채널(Short Channel) 현상으로 인해 더 이상 채널 거리를 좁히기는 무리가 있음.

2) 이에 대한 대안으로 현재 DRAM에서의 미세화는 캐패시터(Capacitor)에서 발생하고 있으며, 캐패시터 내 전하 저장량을 늘리는 정전용량(Capacitance)을 높이는 것이 공정 목표임.

3) 정전용량을 높이는 방법은 캐패시터의 밑면 길이를 좁히거나, 높이를 높이거나, 유전상수를 높이는 방법 3가지가 있음.

4) 그러나 현재 캐패시터는 종횡비 (Aspect Ratio)의 증가로 한계를 맞이했으며, 남은 방법은 유전상수 K를 높이는 것으로 K 값을 적정 수준으로 높이기 위해 생산업체들은 여러 물질을 배합함.

5) 지르코늄-하프늄-지르코늄, 지르코늄-하프늄-티타늄 등의 순으로 물질을 캐패시터에 얇게 증착하며, 어떻게 물질을 배합할 것인지 가 생산업체들의 고유 Recipe임.

6) 1a, 1b, 1c 등 미세화가 진행되는 과정에서 당초 계획보다 더디게 진행되고 있는 핵심 배경 중 하나에 High-K Capacitor 공정도 포함됨.

7) 생산업체들 공통적으로 Capacitance를 높일 수 있는 새로운 물질 배합을 찾는 과정에서 어려움을 겪고 있으며, 이론적으로 맞는 배합도 실제 공정에 적용했을 때 문제가 발생하는 경우도 있음.

8) 이러한 문제들은 미세화가 되면 될수록 해당 과정의 시간, 난이도 등이 높아지는 점이 어려움을 겪고 있는 배경임.

미세화 대응 방향 - ② 3D 구조화

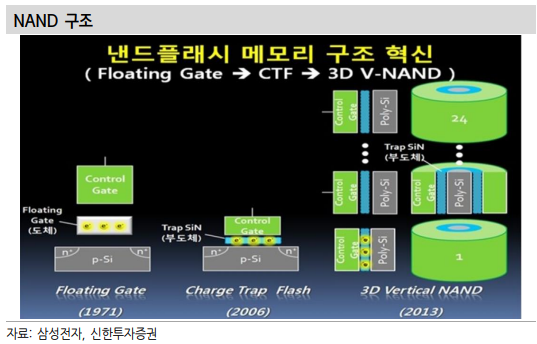

1) NAND에서의 미세화는 단수의 증가로 나타나며, 2013년부터 2D 구조 하에서 선폭 줄이기의 한계점에 도달했고 3D 구조로 변화했음.

2) 3D NAND로의 구조 변화 초반에는 단수의 증가에 큰 기술적 어려움이 없었으나, 고단화가 심화될수록 식각과 증착 난이도 증가에 직면함.

3) 단수가 높아질수록 홀(Hole)의 깊이가 깊어지면서 식각 공정 난이도가 증가하며, 균일하고 올곧게 에칭하는(뚫는) 것이 중요한데, 깊이가 깊어질수록 어렵기 때문임.

4) 아래 쪽 깊은 층들에서 위쪽 얕은층들과 달리 에칭이 불량하게 되는(울퉁불퉁) 문제점이 발견됐으며, 삼성전자는 128단까지 한번에 완벽하게 에칭할 수 있었고, SK하이닉스는 72단부터 에칭에 어려움을 겪었음.

5) 이를 해결하기 위해 2개를 적층하는 Double Stack 방식을 적용했으며, 이는 10단 1개와 20단 1개를 붙이면 30단 1개를 만들 수 있는 원리로 삼성전자는 176단부터 Double Stack을 적용할 예정임.

6) 또한 고단화 될수록 하중이 커지면서 하부층이 휘어 질 수 있으며, 두께가 높아 위아래 높이가 높아지면 전력 소모 역시 크게 발생함.

7) 그래서 막의 두께를 얇게하고 전체 높이를 최소화할 필요가 있으며, ALD 방식의 증착 필요성이 대폭 확대되면서 난이도 뿐만 아니라 생산 소요시간 역시 이전대비 증가했음.

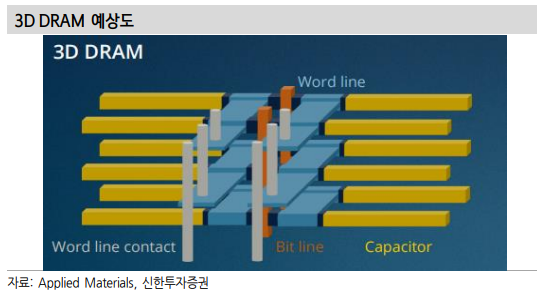

8) DRAM에서도 글로벌 생산업체들은 1d 이후(10나노 이하)부터 3D 구조로 변화를 준비하고 있으며, 이에 맞춰 장비사들 역시 관련 대응을 위해 생산업체들과 함께 연구개발을 진행 중임.

9) 기존 DRAM과 달리 캐패시터를 옆으로 눕히는 방식 등을 통해 적층이 가능하게 하는 등 여러 방식을 준비하고 있으나, 현재 DRAM에서 3D 구조로의 변화가 유일한 미세화 대응 방향은 아님.

미세화 대응 방향 - ③ EUV 도입

1) 공정 미세화 심화 속에서 회로 선폭이 축소될수록 회로 패턴을 그리는 난이도가 높아지며, 빛으로 웨이퍼에 회로 패턴을 그려넣는 포토공정 내에서 DUV(심자외선, ArF) → EUV(극자외선)로의 전환은 필수적임.

2) ArF(불화아르곤) 대비 EUV는 파장이 짧아 14배 가량 더 세밀하게 회로를 그릴 수 있으며, EUV는 DUV 보다 정밀도가 높기 때문에 공정 스텝수 감소가 가능함.

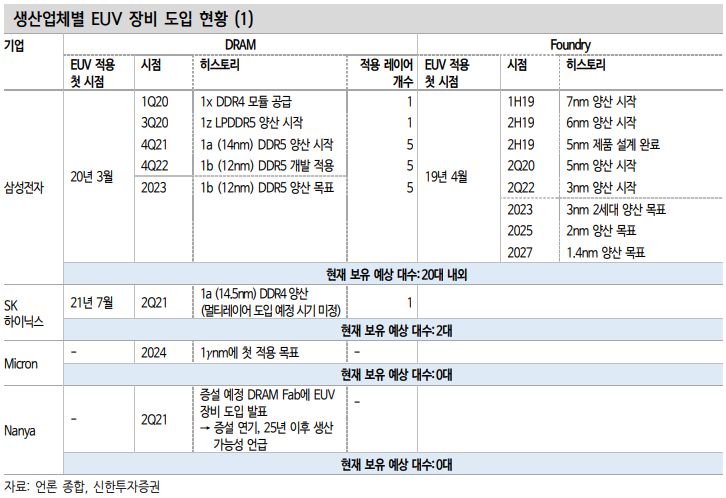

3) 따라서 생산업체들은 EUV 장비 적용을 통해 비용 절감이 가능하며, 글로벌 유일 EUV 장비 제조사인 ASML에 따르면 2020년 EUV 장비 보급 비중은 파운드리 90%, 메모리 10%였음.

4) 주요 반도체 생산업체들은 비메모리에 이어 메모리에서도 EUV 적용을 확대하고 있어, 메모리 적용 비중의 점진적 확대가 예상됨.

5) 삼성전자는 20년 8월부터 P2(평택 2라인) 1z에 도입했으며, 현재 DRAM(LPDDR5)을 양산 중으로 21년 10월부터 1a에도 적용해 DDR5 제품 양산 확대를 밝혔음.

6) SK하이닉스는 M16(이천) 1a부터 도입했으며, 1b, 1c로 가면서 생산업체들의 EUV 적용 레이어가 소수의 공정 위주로 점진적 확대될 전망임.

7) 업체별 EUV 도입속도가 다른 상황에서, 메모리에서도 EUV 장비의 선제적인 도입을 통해 원가 경쟁력을 갖춰가는 업체들과 그렇지 않은 업체들간의 격차가 확대될 것으로 예상됨.

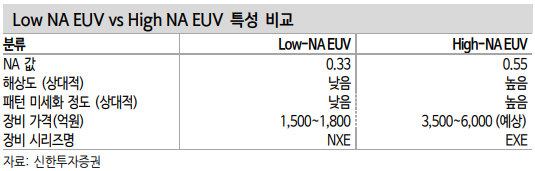

8) 차세대 장비인 High-NA EUV 장비는 인텔이 업계 최초로 적용하겠다고 밝혔으며, NA는 Numerical Aperture의 약자로 NA 값이 높아질수록 EUV 빛을 많이 모아 해상도가 좋아지기 때문에 미세한 회로를 그릴 수 있음.

9) 기존 Low-NA 장비의 NA 값은 0.33이었지만 현재 생산되고 있는 High-NA 장비의 NA 값은 0.55 수준이며, ASML은 23년 첫 장비를 6대 생산할 예정이고 향후 장비 가격은 3,500~6,000억원으로 증가할 것임.

미세화 대응 방향 - ④ GAA 구조(MBCFET)

1) 반도체 트랜지스터의 구조는 지속 변화해왔으며, 2차원 PlanarFET 구조의 대표 제품이었던 MOSFET에 이어 3차원 구조의 FinFET, GAA로 발전 중임.

2) 트랜지스터의 동작 전압을 좀 더 낮추는데 한계를 맞이할 때마다 새로운 구조로의 기술 개발이 필요했으며, 동작 전압이 낮아져야 발열과 전력 소모량을 줄일 수 있음.

3) FinFET 구조에서 한계점은 4나노였으며, 4나노 이하에서 동작 전압을 낮추는 것이 불가능해지면서 새로운 트랜지스터 구조가 필요해졌음.

4) 이 때 나온 것이 GAA이며, GAA(Gate All Around)는 FinFET 구조와 마찬가지로 3차원 형태이면서 FinFET 대비 게이트와 채널이 닿는 면적수가 4개로 늘어남.

5) 게이트와 채널이 닿는 면적이 넓어질수록 전력 효율이 높아지며, 단채널 현상을 개선시키는 것과 동시에 전력 효율 측면에서도 긍정적 효과가 발생함.

6) 삼성전자는 일반적인 GAA 구조에서 좀 더 발전된 형태의 MBCFET을 개발했으며, GAA 구조의 일반적인 형태는 Nanowire 형태로 채널이 가느다란 구조임.

7) 이 경우 채널의 폭이 좁아져 대량의 전류를 흐르게 하기 제한적이며, 이러한 점을 보완한 MBCFET(Multi-Bridge Channel Field Effect Transistor)은 Nanosheet 형태임.

8) 채널과 닿는 면적을 넓게 만들면서 일반적 GAA 구조 대비 많은 양의 전류를 흐르게 할 수 있으며, MBCFET은 기존 FinFET 대비 소비전력 50% 절감, 성능 30% 개선, 공간 차지 45% 축소가 가능함.

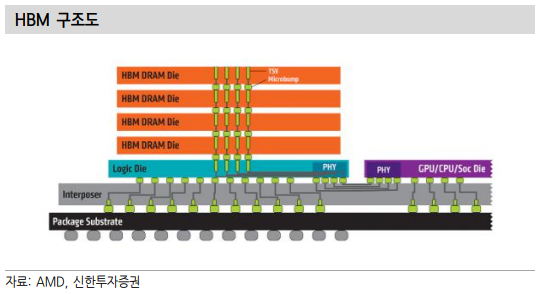

차세대 제품 개발 - HBM, PIM, CXL

1) HBM : HBM은 High Bandwith Memory의 약자로 고대역폭 반도체라는 뜻으로 TSV 기술(Through Sillicon Via)을 적용해 여러 개의 DRAM 칩에 미세한 구멍을 뚫어 수직으로 연결한 형태임.

2) 장점은 성능은 올리면서 동시에 크기는 줄일 수 있다는 점이며, 많은 양의 데이터 전송 과정에서 병목현상이 발생하지 않고 빠르게 전달이 가능하기 때문에 AI, 슈퍼컴퓨터, 고성능 서버 등에 적용될 전망임.

3) 병목현상 없이 데이터 병렬처리가 가능한 배경은 DQ(입출력 data path)가 많기 때문이며, 일반적인 DRAM은 칩 하나당 8개, 모듈 단위인 DIMM 기준으로 64개의 DQ를 가지고 있는 반면, HBM은 1,024개의 DQ를 가지고 있음.

4) SK하이닉스가 2013년 최초로 HBM을 개발했으며, 현재 HBM3(12단) 양산까지 성공했음.

5) PIM : PIM은 Processing in Memory의 약자로 기존 메모리의 저장기능과 함께 연산기능이 추가된 반도체를 말하며, PIM 구조의 반도체가 개발된 배경은 병목현상 확대에 있음.

6) DRAM에서 전달하는 데이터가 CPU에 도달하면 연산 처리를 하는데, 데이터 양이 증가하면서 DRAM-CPU 구간의 병목 현상이 발생하므로 일부 데이터를 DRAM 내에서 연산 처리하는 방식이 채택됨.

7) CXL : CXL은 Compute Express Link의 약자로 새로운 차세대 인터페이스를 말하며, PCle(Peripheral Commponent Interconnect Express)을 기반으로 용량 확장이 가능하다는 점이 핵심임.

8) 기존 서버의 구조를 바꾸지 않은 상태에서 인터페이스 개선을 통해 SSD처럼 장착을 통해 용량을 확장시킬 수 있으며, 2021년 삼성전자가 최초로 CXL 메모리 솔루션을 출시했음.

'리포트 > 반도체' 카테고리의 다른 글

| [필독] 반도체 산업 리포트 : 반등의 역사 - 새로운 수요의 중심, 비메모리 (0) | 2023.04.27 |

|---|---|

| [필독] 반도체 산업 리포트 : 반등의 역사 - 중기적 메모리 Cycle 미리보기 (수요) (0) | 2023.04.27 |

| [필독] 반도체 산업 리포트 : 반등의 역사 - 교훈의 적용, 23년 Cycle에 대한 해답 찾기 (0) | 2023.04.26 |

| [필독] 반도체 산업 리포트 : 반등의 역사 - 네 차례 Cycle의 교훈 (0) | 2023.04.26 |

| 반도체 산업 리포트 : 추가 감산의 추억 (0) | 2023.04.25 |

댓글