▼ 2024 이공계 대기업 취준생 멘티 모집 中

[이공계 대기업 취업 멘토링] 2024 삼성그룹 상반기 멘토링 서류 합격률 결과

[2024 이공계 대기업 취업 멘토링] 이공계 대기업 취준생 멘티 모집 이공계 대기업 취준생 멘티 모집 SK하이닉스/삼성전자를 비롯하여 이공계 대기업의 엔지니어 직군으로 입사를 희망하는 분들

feeling-stock.tistory.com

삼성전자 공정설계 직무면접 기출 답안 (느낌이 블로그)

들어가면서

안녕하세요, 느낌이입니다.

GSAT 일정이 종료되고 쉴틈없이 바로 면접준비를 하고계실 모든 취준생 여러분들을 응원합니다.

이번 글에서는 삼성전자 메모리 공정설계 직무에 재직중인 현직자분의 직무 필기노트를 여러분들께 공유드리고자 합니다.

전공 및 PT 면접에서는 정답이 명확하고 체점 기준이 분명하므로, 해당 문제들을 정확히 해결하는 부담감이 있습니다.

하지만, 반도체 공정과 본인 전공에 대해 깊이 있는 공부를 해오신 분들이라면 충분히 풀 수 있는 난이도인데요.

이 자료가 삼성전자 DS 공정설계 및 SK하이닉스 소자 직무에 지원하시는 모든분들께 유용하게 사용된다면 좋을 것 같습니다.

1. EUV : 13.5nm의 극자외선 파장을 이용한 노광 공정

1) R(resolution) : Resolution이란 포토 공정을 통해 구현해낼 수 있는 최소 미세 선폭의 한계

2) 노광 설비 발전의 역사

G-line(436nm) → I-line(365nm) → KrF(248nm) → 193nm(ArF) → EUV(13.5nm) 구현 (ArF-i는 38nm급)

3) EUV 특징 : 파장이 매우 짧고 에너지가 매우 높음. 또한 매질에 흡수율이 매우 높아 공기에서도 흡수되는 단점으로 인하여 기존 포토 공정의 렌즈 투과 방식을 사용할 수 없음.

이로 인하여 EUV 장비의 광학계는 빛을 투과하는 것이 아닌 반사 거울을 통해 웨이퍼까지 이동시켜 노광. 광학계 반사 거울들의 align 중요. Mask 또한 투과형 mask가 아닌 반사형 mask로 기존 mask 물질과 다름.

Mask pellicle에서도 광원이 흡수되는 단점이 있으며, 현재 많은 업체들이 pellicle의 투과율을 90프로 이상을 목표로 개발하는 단계에 있음.

(Mask 들어갈 때, 나올 때 2번의 투과를 거치면 실제 투과율은 더 떨어지게되어 웨이퍼에 정확한 빛의 양을 도달하기에 Risk가 있음.)

6) DRAM의 EUV 적용 : 업계 최초 14nm 디램 일부 LAYER에 EUV를 적용 (20년 3월 17nm급 DRAM에 첫 EUV 적용을 이후로 21년 10월 14nm DDR5로 양산에 본격 적용.)

7) EUV 공정 도입을 통해 집적도 향상, 소자 미세화, 소비전력, 동작속도, 성능 개선이 가능함.

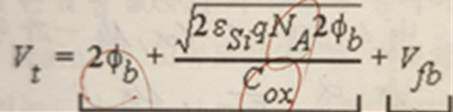

2. MOSFET의 동작

1) MOSFET은 MOS 캐패시터를 이용하여 이에 S/D 단자를 통해 전류를 흐를 수 있도록 만든 트랜지스터 소자임.

2) Cut off 영역 : Gate 전압이 vth보다 낮은 영역으로 채널이 형성되지 않은 영역임.

3) Linear 영역 : Gate 전압을 vth보다 높게 인가하면 채널이 형성되고, Gate와 Drain 전압을 증가시킬수록 전류의 양이 증가하는 영역임.

4) Pinch off 영역 : Drain의 전압을 계속 증가시켰을 때, 어느 순간 Drain의 Depletion 영역으로 인하여 Channel 일부가 잠식되는데 이는 Channel과 Drain 접합이 끊어지는 순간과 같음.

5) Saturation 영역 : 채널이 끊겼지만, Drain의 높은 전계의 영향으로 채널의 전자를 Drain까지 터널링으로 이동시킬 수 있게됨.

하지만 Drain 전류를 더이상 증가시킬 수 없으며, 오직 Gate 전압에 의해서만 전류가 증가하는 구간임.

6) Channel length modulation : 실제 Sat 구간에서 Drain의 전압이 아예 영향을 주지 않는다는 것은 엄밀히 말하면 틀린 말임.

그 이유는 Drain의 Depletion 영역이 channel의 일부를 잠식하면서 Channel의 Effective length는 줄어들게 되고 이는 실제 미세화된 소자에서 Saturation 영역의 전류를 증가시킴.

3. SCE (Short Channel Effect)

1) 반도체 소자의 미세화를 통해 집적도를 높이며 Channel length를 줄이면서 소비 전력과 동작 성능을 높일 수 있음.

하지만 Channel length가 줄어듬에 따라 동반되는 비이상적인 효과가 Short channel effect 임.

2) DIBL (Drain Induced barrier lowering) : Drain 전압의 영향으로 Effective channel length의 감소로 인하여 문턱 전압이 낮아지는 현상임.

Drain의 전압이 걸리면 기판과의 PN 접합의 역방향 Bias로 인하여 기판쪽으로 공핍층의 확장(Drain 고농도, 기판 저농도)이 발생하여 채널 영역을 잠식하며, 그 결과 실제 Effective channel length는 감소하여 문턱 전압이 낮아지게 됨.

3) Punch through : Drain 전압으로 인하여 Drain과 기판간 발생한 Depletion 영역이 Source의 Depletion 영역과 만나게되어 Current path를 형성하게 되고, 이 Path로 인하여 Cut off 영역에서 누설 전류가 증가하게 되는 현상임.

*문턱 전압이 낮아지면 DIBL/ 누설 전류가 발생하면 Punch through.

Drain의 depletion region의 확장이 원인이며, Drain과 기판 사이에 국부적인 영역에 기판과 같은 극성의 고농도 도핑으로 Depletion region 확장을 억제하여 DIBL과 Punch through를 개선할 수 있음. (Halo 이온 주입)

4) Depletion region : N type 반도체와 P type 반도체가 접합을 하였을 때, 각 Carrier인 전자와 정공이 Diffusion 및 Recombination으로 Carrier가 존재하지 않는 영역임.

이 영역에서는 전자와 정공의 빈자리에 움직이진 못하지만 빠져나간 전자와 정공으로 인하여 극성을 띄는 이온 형태로 고정되어 있음.

5) HCI (Hot carrier injection) : 채널 길이가 짧아짐에 따라 Drain 전계의 영향으로 Channel의 Carrier가 가속되고 높은 에너지를 갖게 되는데, 이렇게 고속, 고에너지의 Carrier를 Hot carrier라 부름.

이 Hot carrier가 Drain 부근의 si 결정들과 충돌하면서 일부 산화막으로 유입되어, 그 유입된 전자의 누적이 증가하면서 결국 소자 특성에 악영향을 끼치게 되는 현상임.

* 일부는 Avalache BV를 일으켜 소자를 파괴함. (Vth 증가, idsat 감소)

6) Avalanche BV : 실리콘 결정과 충돌하여 Impact ionization이 일어나고 이로 인해 Avalanche breakdown이 발생함.

7) impact ionization : 가속된 전자가 실리콘 결정 격자와 충돌하면서 electron hole pair를 발생시킴.

EHP 역시 고에너지를 갖고 주변 실리콘 결정 격자와 충돌하며 계속해서 EHP를 만들어내고 결국 전류의 지수적 증가로 인하여 결국 소자가 터지게 되는 현상이 Avalanche Breakdown 임.

고농고 Drain, Source 부근의 이와 같은 극성의 저농도 도핑을 통해, 전계를 낮추고 과속을 방지하여 HCI를 개선할 수 있음. (LDD : Lightly doped drain, LDD → SPACER → NSD, PSD)

4. HKMG (High k Metal Gate)

1) 반도체가 미세화 되면서 channel length뿐만 아니라, 산화막의 두께도 감소하고 있음.

2) TR 동작 전압을 낮추기 위해 기존 산화막 물질을 점점 얇게 만드는데, 기술적 한계와 산화막 Tunneling issue로 유전율이 높아 두께의 마진을 보완한 새로운 High k dielectric (HfO2 : 25)을 Gate 산화막에 적용함.

* Capacitance가 높다는 것은 전자를 끌어모을 수 있는 능력이 좋다는 것으로 문턱 전압이 낮아짐.

3) HKMG는 이미 파운드리 사업부에서 쓰고 있었으며, 디램에서도 Scaling down에 따라 산화막에 의한 누설 전류와 전력 문제가 생기자 이를 메모리 사업부에서도 적용함.

* 파운드리, 메모리 사업부간 공정 기술력의 공유가 가능한 삼성전자의 경쟁 우위 장점 어필 요소임.

정리하자면,

4) 문제점 : 산화막 두께를 낮추는데 기술적 한계가 발생하며, 매우 얇아진 산화막의 두께로 Tunneling이 발생하여 Gate 누설 전류 증가함.

5) 해결 : 결국 산화막의 두께 감소가 아닌 높은 유전율을 갖는 산화물을 채택하기로 결정함. 이로 인하여 두께를 더 이상 줄이지 않고도 유전율을 높일 수 있게됨

* (High-k, 하프늄 : 25)로 Capacitance를 증가시켜 동작 전압 개선

6) Side effect : 기존 실리콘 Gate로 채널 영역의 전계 전달 균일도가 Bad, 채널 형성이 불규칙하여 Vth의 산포 또한 나쁨. 결국 Channel 영역에서 전자의 Scattering 발생함.

5. ARF immersion + Multi patterning

1) ARF immersion 기법 : 광이 지나가는 렌즈와 Wafer 사이에 기존 공기의 매질이 아닌 굴절율이 높은 물을 매질로 사용하여 Photo 공정의 NA 값을 증가시켜 Resolution 향상한 기법임. (DOF의 허용 범위 내에서)

기존 ARF의 193nm 파장을 134nm 가량 줄일 수 있는 효과를 볼 수 있으며, Resulotion은 38nm까지 낮출 수 있음.

2) 단점 : 물을 사용함에 따라 Wafer나 렌즈에 오염이 발생할 수 있음.

3) Multi patterning : ARF immersion 기법으로 38nm의 resolution까지 가능했지만, 실제 이보다 더욱 미세화된 Pattern을 위해서 Patterning을 여러 번하는 노광 기법을 Multi patterning이라 함.

* LELE : 더블 패터닝 / SADP : Self Align 더블 패터닝

4) LELE : 동일 LAYER를 여러 번 노광하여 Resoltion 향상시킬 수 있으며, 시스템 반도체에 사용됨.

패터닝 개수만큼 Hard mask가 필요함.

두 번의 Hard mask 층 증착 → 맨 윗 층의 Hard mask에 노광 및 에치를 진행 → 이후 다시 Hard mask 증착 후 첫 번째 패턴과 패턴 사이에 Align하여 노광 및 에치를 진행 → 남은 Hard mask pattern이 후속 에치의 mask 가 됨.

5) SADP : 한 번의 결정적인 노광을 통해 Spacer를 형성시킨 후, 이를 Mask로 사용하여 하부 막질을 에치함.

1개의 Hard Mask로 2배, 4배의 Patterning으로 Resolution를 향상시킬 수 있음.

두 번의 Hard mask 층 증착 → 맨 윗 층의 Hard mask에 노광 및 에치로 Pattern 형성 → 형성된 Pattern에 절연막 증착 후 수직 방향 Dry etch를 진행 → Hard mask pattern과 그 측벽에 Spacer를 형성시킴 → Spacer 가운데 기존 Hard mask 영역을 날림 → 이후 Spacer를 mask로 하부 막질을 식각함.

6) SAQP : SADP 공정에서 한번 더 Spacer를 형성하여 4배의 Pattern을 만드는 공정으로, 디램의 SADP는 약 20nm Resolution 수준이지만 SAQP는 약 10nm Resolution 수준으로 10nm급 DRAM 공정에 쓰이고 있음.

두 방식은 모두 포토공정의 해상도 향상 기술이지만 공정방법 차이에서 기인한 패턴 자유도의 차이가 있으며, SADP 방식은 비교적 패턴이 규칙적이고 직선 형태의 배열을 갖는 경우에 주로 사용함.

* Line과 Space가 규칙적이고 직선으로 배열된 메모리 제품에 적용되며, LELE는 불규칙적이고 직선 형태가 아닌 패턴에도 사용할 수 있기 때문에 주로 패턴이 불규칙한 로직제품에 많이 사용함.

7) LELE 장단점 : 기존 노광,식각을 여러번 진행함으로 새로운 기법이 필요 없음.

패턴 자유도가 높아 불규칙 패턴에 용이하나, 여러 개의 mask와 여러 번의 노광 공정 필요함.

8) SDAP 장단점 : 1장의 Hard mask를 사용하여 높은 정렬도를 가지지만, Spacer의 증착과 식각, CMP 공정 추가로 이에 대한 공정 최적화가 필요함.

9) 결론적으로 Multi patterning 기술을 사용하면 EUV 없이 10nm급 메모리를 양산할 수 있지만, 패터닝 숫자, 공정 Step 수 증가로 공정 시간이 늘어나며 생산성 측면에서 단점이 있음.

6. 디램과 낸드플래쉬

1) 디램 : 디램은 1T 1C의 구조를 갖은 휘발성 메모리이다. DRAM Cell에 있는 캐패시커에 전자를 충전 및 방전하면서 Data 1과 0을 저장함.

2) 디램의 동작

Write : WL와 BL에 전압을 인가하여 Cell 캐패시터의 전자를 충전. WL에 전압을 인가하여 DATA가 흐를 수 있는 통로를 열고 BL에 VDD를 인가하면 1을 저장, BL에 VSS를 인가하면 0을 저장함.

Read : Cell 캐패시터에 저장된 data가 무엇인지 읽는 동작임. Pre charge/Charge sharing/Sense amplify/Restore의 4가지 순서를 통해 DATA를 Read 함.

Pre charge : BL에 병렬로 연결된 캐패시터를 VDD/2 만큼만 충전함. (기준 전압이 됨.)

Charge sharing : WL에 전압을 인가하여 transitor를 ON 시킨 후 BL 캐패시터와 Cell 캐패시터 간 전하량를 공유함.

이때 BL 캐패시터가 VDD/2이므로 Cell에 1이 저장되어 있었다면 BL 캐패시터는 전압이 증가 / 0이 저장되어 있었다면 BL 캐패시터는 전압이 감소함.

Sense Amp : BL 캐패시터의 충전량 변화를 주변의 Cell의 BL 캐패시터와 비교를 통해 전압 차이를 증폭 시킴.

증폭시킨 전압이 높아진 경우에는 High (1)이 나오고, 오히려 전압이 낮아진 경우에는 LOW(0)이 나온다.

Restore : Read한 Data를 Cell에 다시 Write함.

Refresh : 캐패시터는 시간이 흐르면 전하가 누출되기 때문에 기존의 Data를 잃지 않기 위해서 Refresh라는 동작을 함.

Refresh는 전력이 소모되고, Refresh 기간 동안 Write, Read 동작에 제한이 생기기 때문에 Refresh 주기를 길게하는 것이 중요함.

이는 Capacitor의 용량을 키워야하는 이유이기도 함.

* Q=CV이며 Capacitor의 용량이 크다면, 1에서 0으로 바뀌게 되는 오류의 시간을 늘려 Refresh 주기를 늘릴 수 있음.

3) 디램 공정의 발전 방향 : Cell의 집적도를 높이기 위해 Size를 줄이는 것이 디램 공정 발전 방향의 기본임.

삼성전자는 최근 업계 최초로 DDR5 기준 5개 레이어에 EUV 노광 공정을 채택하였으며, 10nm급 DDR5를 양산시켜 집적도를 높였음.

Cell Size를 감소시키는 동시에 Capacitance의 용량은 증가시키기 위해서 High aspect ratio ETCH가 필수적임.

결국 막질 Depo.의 균일성 또한 중요해지므로, 디램 세대가 지날수록 각 단위 공정 기술 난이도가 어려워짐.

4) 낸드플래쉬 : 1개의 Transitor를 통해 만들어지는 비휘발성 메모리이며, 2개의 Gate와 2개의 oxide로 이루어짐.

* Control gate/Blocking oxide/Floating gate/Tunneling oxide 구조.

디램과는 다르게 기존 상태가 1의 값이고 data를 저장한 상태가 0임.

5) 낸드의 동작

전자를 저장하여 0의 상태가 되는 것을 Program이라 하며, 전자를 방전시켜 본래 1의 상태가 되는 것을 Erase라 함.

Program : Control gate에 높은 전압을 인가하여 이 전계가 Body에 있는 전자들을 Floating gate까지 끌어당겨서 전자를 저장함.

Erase : 기판에 높은 전압을 인가하여 Floating gate에 저장된 전자를 빼내어 본래 1의 상태로 되돌아감.

Read : 낸드플래쉬의 Transistor에 적당한 전압을 인가하였을 때, S/D 사이에 전류가 흐르는지 확인하여 Cell의 상태가 1인지 0인지 판단함.

Program된 상태라면 FG에 전자가 저장되어 있으며, CG에 약전압을 인가하면 FG의 전자들에 의해 전계의 전달력이 떨어져서 전류가 흐르지 않음.

이 상태를 Vth가 High 한 1이라고 말하며, 반대로 전자가 저장되지 않았다면 CG에 약전압을 인가해도 전류가 흐를 수 있는데 Vth가 낮은 0의 상태임.

결국 전류가 흐르면 1, 흐르지 않으면 0임.

6) SLC/MLC/TLC : 1개 Cell에 저장량을 늘리는 기술임. (전자의 충전량을 미세하게 조절)

한 개의 Cell 용량을 늘릴 수 있으나 Vth간 마진이 부족해지므로, 이에 정확히 Data를 읽고 쓰는 난이도가 높아짐.

속도적으로도 SLC → MLC → TLC로 갈수록 부족함.

7) 낸드의 공정 발전 방향 : FG(poly silicon) → Charge trap flash

낸드도 마찬가지로 Cell과 Cell간의 거리가 가까워지면서 상호 간섭이 발생함.

이를 보완하기 위해서 부도체인 Silicon nit 막질로 변경했으나, 집적도 문제와 해결되지 않는 Cell간 상호 간섭으로 인하여 수평적 Cell 배열이 아닌 수직 적층 구조로 만듦.

낸드에서도 CG Gate와 Blocking layer간 Tunneling 방지를 위해서 MKMG 적용함. (TaNOS)

수직적 적층 구조 도입을 통해 DRAM에 비해선 수평적 미세화가 덜 필요하여 EUV 도입 계획은 아직 없음.

하지만 고층 적층 구조 공정 진행 시, High aspect ratio 의 Etch 및 Depo. 공정 난이도 매우 높음.

[2024 이공계 대기업 취업 멘토링] 이공계 대기업 취준생 멘티 모집

이공계 대기업 취준생 멘티 모집 SK하이닉스/삼성전자를 비롯하여 이공계 대기업의 엔지니어 직군으로 입사를 희망하는 분들을 위해 삼성전자 DS부문의 현업에 있는 멘토 두 명이 멘티의 취준을

feeling-stock.tistory.com

▼ [전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ①

[전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ①

들어가면서 반도체 직무/전공 면접 관련해서 제가 공부했었던 반도체 소자 내용들을 함께 공유해보려고 합니다. 많은 취준생 분들께 도움이 됐으면 좋겠습니다. 문의사항은 댓글로 남겨주세요.

feeling-stock.tistory.com

▼ [전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ②

▼ [전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ③

[전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ③

들어가면서 반도체 직무/전공 면접 관련해서 제가 공부했었던 반도체 소자 내용들을 함께 공유해보려고 합니다. 오늘은 SCE을 개선할 수 있는 방법에 대해 중점적으로 다뤄보겠습니다. 본 내용

feeling-stock.tistory.com

▼ [전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ④

[전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ④

들어가면서 반도체 직무/전공 면접 관련해서 제가 공부했었던 반도체 소자 내용들을 함께 공유해보려고 합니다. 오늘은 소자 관련 심화 내용을 한번 다뤄보겠습니다. 본 내용들은 질문의 핵심

feeling-stock.tistory.com

▼ [전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ⑤

[전공 면접] 삼성전자 공정설계 / SK하이닉스 소자 직무˙전공 면접 예상 문제 ⑤

들어가면서 반도체 직무/전공 면접 관련해서 제가 공부했었던 반도체 소자 내용들을 함께 공유해보려고 합니다. 오늘은 메모리반도체 관련 내용을 한번 다뤄보겠습니다. 본 내용들은 질문의 핵

feeling-stock.tistory.com

'느낌이 취업 스터디 > 면접 기출' 카테고리의 다른 글

| [삼디플 공채] 삼성디스플레이 직무 및 인성면접 기출 문제 (41) | 2024.05.03 |

|---|---|

| [삼스디 공채] 삼성SDI 직무 및 인성면접 기출 문제 (47) | 2024.05.01 |

| [아스믈 공채] ASML 직무 및 인성면접 기출 문제 (26) | 2024.04.25 |

| [디스플레이] LG디스플레이 패널설계 / 삼성디스플레이 패널설계 직무˙전공 면접 기출 문제 ④ (48) | 2023.10.08 |

| [디스플레이] LG디스플레이 패널설계 / 삼성디스플레이 패널설계 직무˙전공 면접 기출 문제 ③ (58) | 2023.10.07 |

댓글